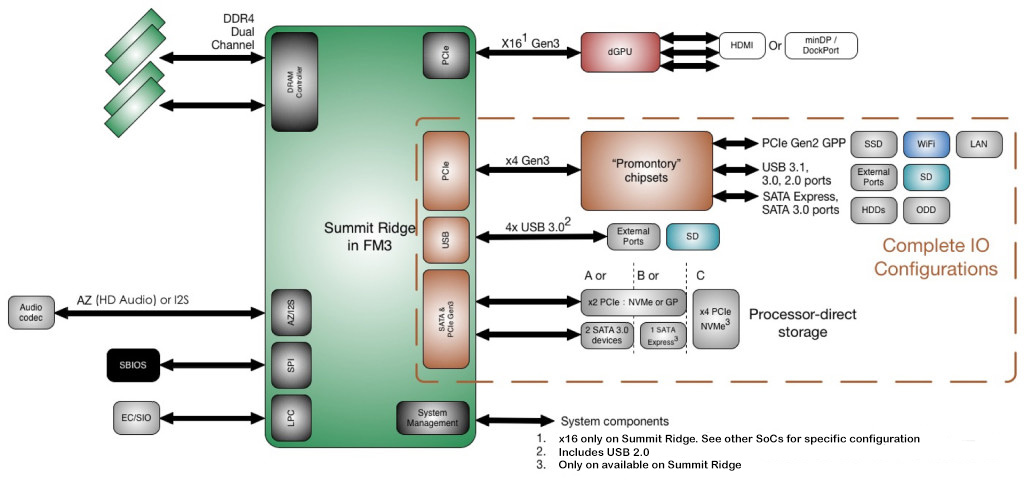

Not quite. You're limited to a single x8 or single x16 (although if that *can't* be split x8/x8 for multi-GPU I'd be amazed) Gen 3 for dGPU. If you're using a chipset, you get 4 or 6 PCIe gen 2 lanes for peripherals and slots; if not you

might be able to use the 4 Gen 3 lanes that usually make up the chipset link (that's not exactly clear). You can always pull off an additional 2 PCIe gen 3 lanes from the storage cluster, but doing so loses you the option of NVMe. So with Bristol Ridge and a chipset (or at least, with the announced chipsets) you have a maximum of 10 PCIe gen 3 lanes (8 of which are a dedicated cluster for dGPU) + 6 PCIe gen 2 lanes - so you could, for instance, have a PCIe3 x8, 2 PCIe 3 x1, a PCIe 2 x4, and 2 PCIe 2 x1 - giving a total of 6 slots (but not much in the way of additional peripheral chips

).

Skylake actually offers less PCIe from the CPU than Summit Ridge - it ONLY does 16 lanes (although it's flexible about how they can be split down). OTOH, the Z170 claims to offer up to 20 PCIe 3 lanes (they get shared out amongst the various peripherals the chipset supports): but since the chipset connects using the same PCIe 3 x4 link that AMD uses, you'd struggle to feed all 20 of those lanes simultaneously.

Assuming you mean the IGP, not as far as I know. They shared a memory controller and have other direct linkage - they don't need an external bus.

LinkBack URL

LinkBack URL About LinkBacks

About LinkBacks

Reply With Quote

Reply With Quote