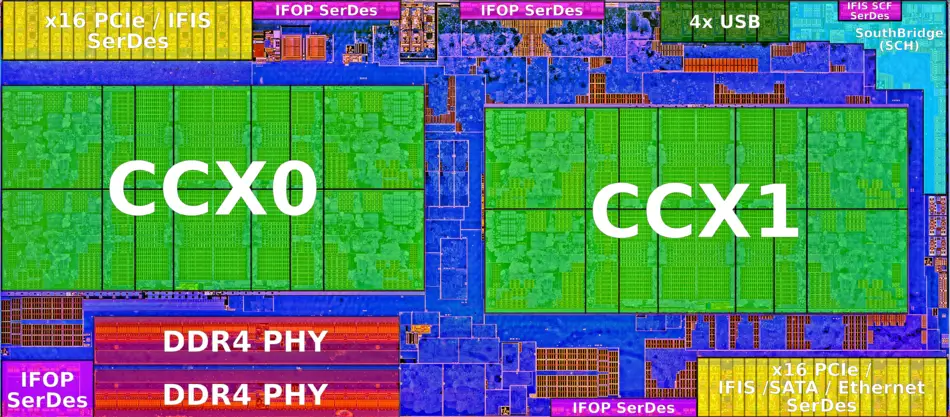

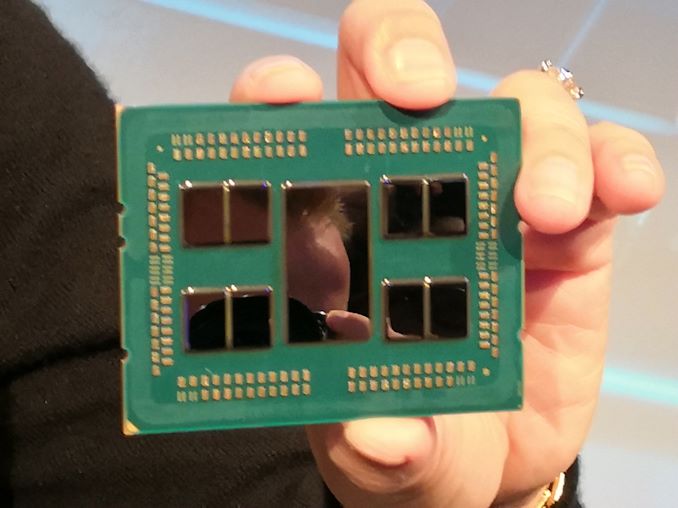

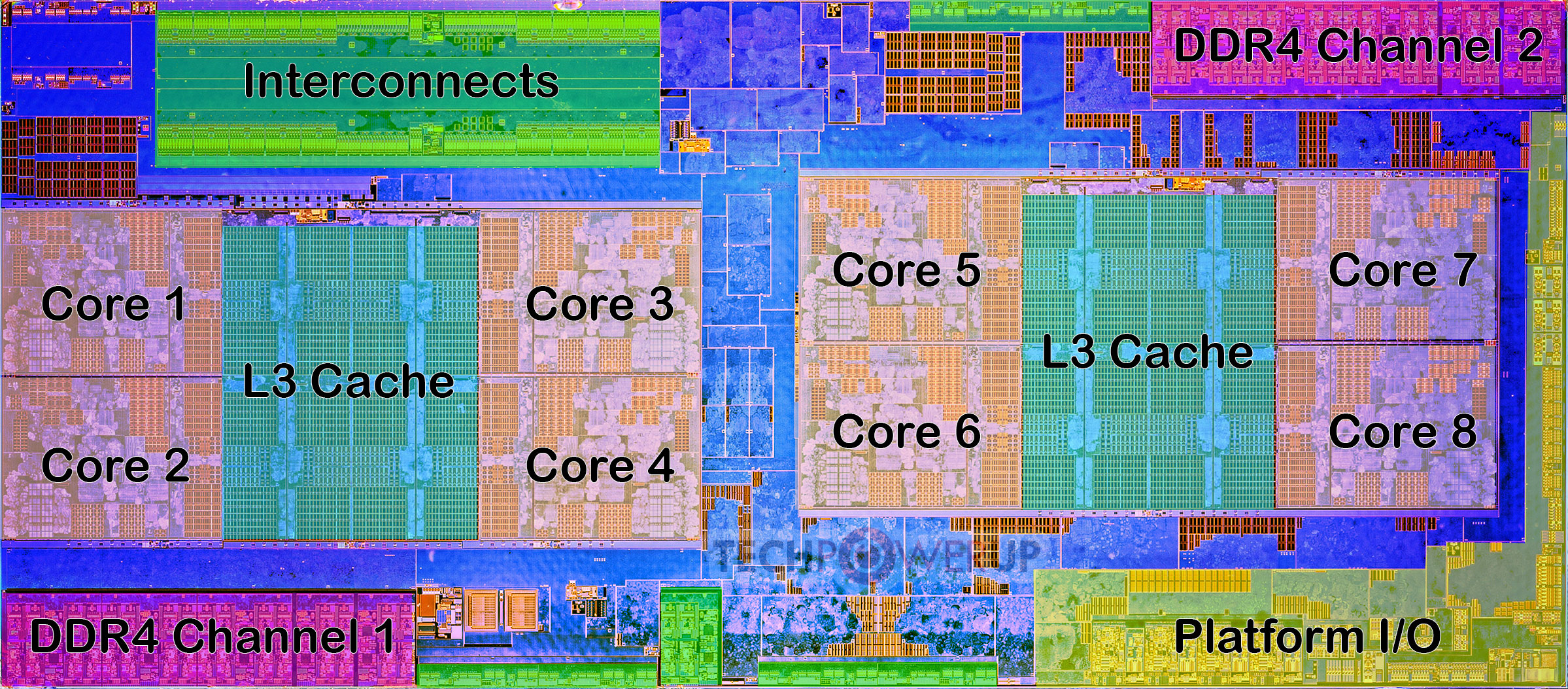

In terms of routing 8x8 dies, using a separate chip, makes sense as it removes the traces from the imposter and onto the die. But it also means am4 will and potentially tr will get separate io chips.

That is the only disadvantage and potential different latencies with the chiplets in that config.

upside

faster clock speeds

Chiplets can be used in am4/tr4/sp3 without any changes and no unused features..

I do think maxon now needs to release cinebench r20 ..

the scene used just doesn't cut it for TR upward

LinkBack URL

LinkBack URL About LinkBacks

About LinkBacks

Reply With Quote

Reply With Quote

the scene used just doesn't cut it for TR upward

the scene used just doesn't cut it for TR upward